gem5 and CXL

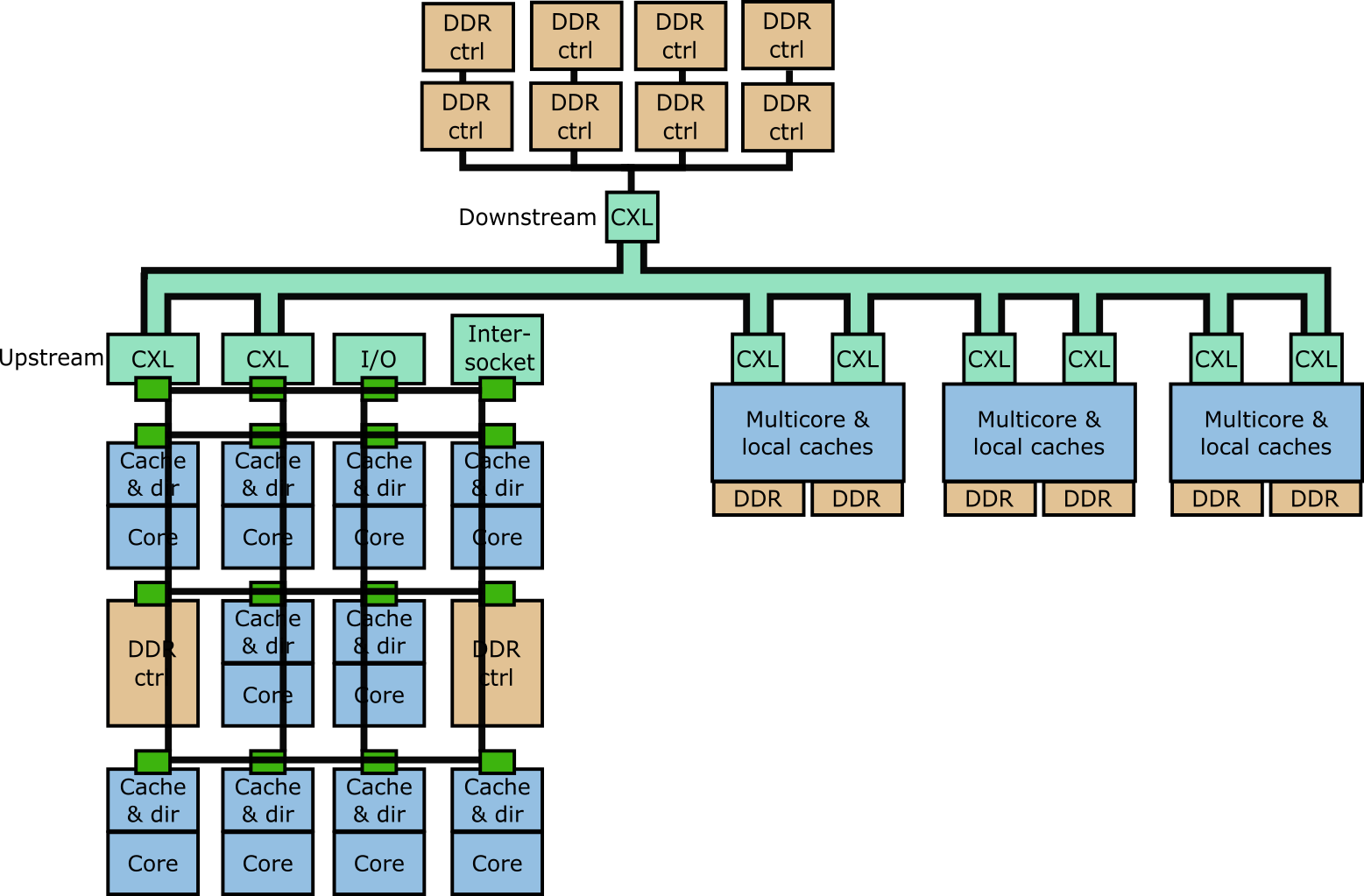

The Compute Express Link (CXL) is a new high-speed interconnect that allows for attaching memory and accelerators to a host processor. One of the potential applications of CXL is disaggregated memory, where memory resources are pooled and shared across multiple compute nodes, allowing for higher memory utilization and scalability. However, this also introduces new challenges and trade-offs in terms of performance, consistency, and security.

This project is developing infrastructure in the gem5 simulator to explore the performance of systems with CXL-based disaggregated memory. We will enable gem5 to run multiple nodes which can share the memory resources of a CXL device. We are also using the SST Simulator to model the CXL device and the network connecting the nodes. Futhermore, SST allows us to use multiple processors or multiple nodes to improve the performance of the simulation.

We will be releasing the source code and publishing a companion paper soon. If you want to be notified when the source is available, please complete the gem5-cxl interest form.